|

CXSD62118单相恒定时间同步的PWM控制器驱动N通道mosfet低压芯片组RAM电源 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

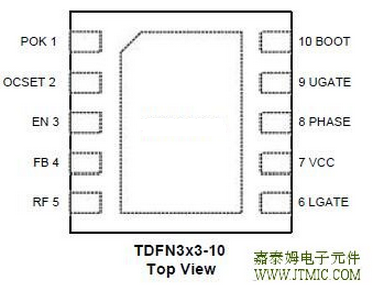

目录 1.产品概述 2.产品特点 一,产品概述(General Description) The CXSD62118 is a single-phase, constant-on-time,synchronous PWM controller, which drives N-channel MOSFETs. The CXSD62118 steps down high voltage to generate low-voltage chipset or RAM supplies in notebook computers. Adjustable Output Voltage from +0.7V to +5.5V Notebook 需要详细的PDF规格书请扫一扫微信联系我们,还可以获得免费样品以及技术支持! 五,产品封装图 (Package)

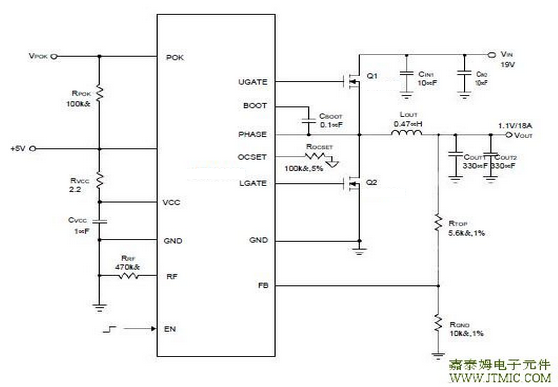

六.电路原理图

七,功能概述 Input Capacitor Selection (Cont.) IOUT/2,where IOUT is the load current. During power-up, the input capacitors have to handle great amount of surge current.For low-duty notebook appliactions, ceramic capacitor is recommended. The capacitors must be connected be-tween the drain of high-side MOSFET and the source of low-side MOSFET with very low-impeadance PCB layout should be used. The design has to trade off the gate charge with the RDS(ON) of the MOSFET: driver will not charge the miller capacitor of this MOSFET.In the turning off process of the low-side MOSFET, the load current will shift to the body diode first. The high dv/dt of the phase node voltage will charge the miller capaci-tor through the low-side MOSFET driver sinking current path. This results in much less switching loss of the low-side MOSFETs. The duty cycle is often very small in high battery voltage applications, and the low-side MOSFET will conduct most of the switching cycle; therefore, when using smaller RDS(ON) of the low-side MOSFET, the con-verter can reduce power loss. The gate charge for this MOSFET is usually the secondary consideration. The high-side MOSFET does not have this zero voltage switch- ing condition; in addition, because it conducts for less time compared to the low-side MOSFET, the switching loss tends to be dominant. Priority should be given to the MOSFETs with less gate charge, so that both the gate driver loss and switching loss will be minimized. The selection of the N-channel power MOSFETs are determined by the R DS(ON), reversing transfer capaci-tance (CRSS) and maximum output current requirement. The losses in the MOSFETs have two components:conduction loss and transition loss. For the high-side and low-side MOSFETs, the losses are approximately given by the following equations: Phigh-side = IOUT (1+ TC)(RDS(ON))D + (0.5)( IOUT)(VIN)( tSW)FSW transition loss.The switching interval, tSW, is the function of the reverse transfer capacitance CRSS. The (1+TC) term is a factor in the temperature dependency of the RDS(ON) and can be extracted from the “RDS(ON) vs. Temperature” curve of the power MOSFET. of the regulator.With power devices switching at higher frequency, the resulting current transient will cause voltage spike across the interconnecting impedance and parasitic circuit elements. As an example, consider the turn-off transition of the PWM MOSFET. Before turn-off condition, the MOSFET is carrying the full load current. During turn-off,current stops flowing in the MOSFET and is freewheeling by the low side MOSFET and parasitic diode. Any parasitic inductance of the circuit generates a large voltage spike during the switching interval. In general, using short and wide printed circuit traces should minimize interconnect-ing impedances and the magnitude of voltage spike. plane construc-tion or single point grounding. The best tie-point between the signal ground and the power ground is at the nega-tive side of the output capacitor on each channel, where there is less noise. Noisy traces beneath the IC are not recommended. Below is a checklist for your layout: nodes since these nodes are fast moving signals.Therefore, keep traces to these nodes as short as Layout Consideration (Cont.) charging and discharging current. The traces from the gate drivers to the MOSFETs (UGATE and LGATE) should be short and wide. possible.Minimizing the impedance with wide layout plane be-tween the two pads reduces the voltage bounce of the node. In addition, the large layout plane between the drain of the MOSFETs (VIN and PHASE nodes) can get better heat sinking. The GND is the current sensing circuit reference ground and also the power ground of the LGATE low-side MOSFET. On the other hand, the GND trace should be a separate trace and independently go to the source of the low-side MOSFET. Besides, the cur-rent sense resistor should be close to OCSET pin to avoid parasitic capacitor effect and noise coupling. · Decoupling capacitors, the resistor-divider, and boot capacitor should be close to their pins. (For example,place the decoupling ceramic capacitor close to the drain of the high-side MOSFET as close as possible.) bulk capaci-tors should be close to the loads. The input capaci-tor’s ground should be close to the grounds of the output capacitors and low-side MOSFET. FB pin traces can’t be close to the switching signal traces (UGATE, LGATE, BOOT, and PHASE). 八,相关产品 更多同类产品......

发表评论

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

发表时间:2020-04-24浏览次数:314

| 最新信息 |

|---|

| (1.)CXLE86296D 五通道高 ... (2.)CXLE86295D 五通道高 ... (3.)CXLE86294E PWM调光LE ... (4.)CXLE86293EI 线性恒流 ... (5.)CXLE86292CI 五通道I2 ... (6.)CXLE86291C 三通道PWM ... (7.)CXLE83205X PWM调光LE ... (8.)CXLE83204XS高精度PWM ... (9.)CXLE83203F:高功率DIP7 ... (10.)CXLE83202F:高精度PWM ... |

| 头条信息 |

|---|