|

LPDDR2/LPDDR3 Termination Regulator CXEP3473 is a 3A sink/source tracking termination regulator. It is specifically designed for low-cost/ low-external component count systems | ||||||||||||||||||||||||||||||||||||||||||

|

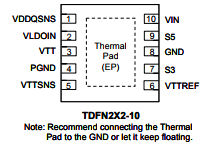

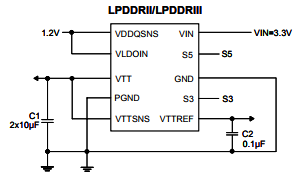

目录产品概述 返回TOP The CXEP3473 is a 3A sink/source tracking termination regulator. It is specifically designed for low-cost/ low-external component count systems. The CXEP3473 maintains a high speed operational amplifier that provides fast load transient response and only requires 20μF (2×10μF) of ceramic output capacitance. The CXEP3473 supports remote sensing functions and all features required to power the LPDDR2 /LPDDR3 /DDR IIIL VTT bus termination according to the JEDEC specification. In addition, the CXEP3473includes integrated sleep-state controls placing VTT in High-Z in S3 (suspend to RAM) and soft-off for VTT and VTTREF in S5 (Shutdown). The CXEP3473is available in the thermally efficient TDFN2X2-10.产品特点 返回TOP „ Support 1.2V LPDDR2/LPDDR3 and DDR IIIL (0.675VTT) Requirements „ Input Voltage Range: 3V to 5.5V „ VLDOIN Voltage Range: 1.2V to 3.6V „ Requires Only 20μF Ceramic Output Capacitance „ Supports High-Z in S3 and Soft-Off in S5 „ Integrated Divider Tracks 1/2 VDDQSNS for Both VTT and VTTREF „ Remote Sensing (VTTSNS) „ ±20mV Accuracy for VTT and VTTREF „ 10mA Buffered Reference (VTTREF) „ Built-In Soft-Start „ Over Current Protection „ Thermal Shutdown Protection „ TDFN2X2-10 Package 应用范围 返回TOP „ DDR IIIL Memory Termination „ LPDDR2/LPDDR3 Memory Termination „ SSTL−2, SSTL−18 „ HSTL Termination 技术规格书(产品PDF) 返回TOP 需要详细的PDF规格书请扫一扫微信联系我们,还可以获得免费样品以及技术支持!

| ||||||||||||||||||||||||||||||||||||||||||

|

DDR Terminator |

|||||||||

|

Part NO. |

VDDQ (V)min |

VDDQ (V)max |

VCNTL (V) |

Isource (A) |

Isink (A) |

IVREF (mA) |

Isupply (μA) |

Note |

Package |

|

1.2 |

3.6 |

3.3~5.5 |

3 |

3 |

10 |

750 |

DDR3/3L,LPDDR2/3 |

TDFN2X2-10 |

|

|

1.2 |

3.6 |

3~5.5 |

1.8 |

1.8 |

-- |

700 |

DDR1/2/3/3L |

SOP8(FD)/MSOP-8(FD) |

|

|

|

|||||||||